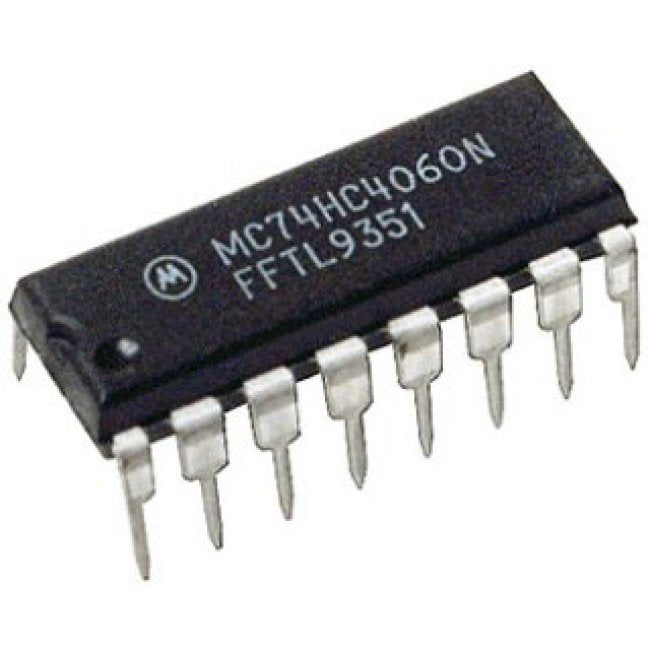

High speed CMOS recommend for High speed CMOS recommend for all new designs. Static sensitall new designs. Static sensitive . Required light decouplinive . Required light decoupling (0.1µF per 20 ICs) With 75-8g (0.1µF per 20 ICs) With 75-80% power reduction compared to0% power reduction compared to standard Schottky.

- Tri-S standard Schottky.

- Octaltate Quad D Register Transparent Latch (3 State)

Please Note: Online stock only for this item. Shipping at checkout for this item may be an estimate only and may apply only to some metro areas or to a specific distance from supply location. Local pickup may be available on some items by prior arrangement. Shipping charges may still apply for this item for Click and collect in store orders as this item may still need to be shipped to us for collection from the local pickup location.

Please use the contact us form to get an accurate shipping quote based on your order quantity and location to avoid order cancellation charges.